为突破 SATA 6Gbps 频宽限制, Intel 正积极推动 NVMe 控制器介面普及,全新 Intel Z170 系统晶片大幅增加内建 PCIe Lanes 数目并升级至 PCIe Gen 3 规格,能配合新一代 Intel SSD 750 U.2 固态硬碟,单颗最高读写速度高达 2.2GB/s Read 、 900MB/s Write , 4K IOPS 最高可达 430,000 ,性能绝非一般 AHCI 规格的 PCIe SSD 可比拟。

NVMe SSD 时代来临 !!

SSD 固态硬碟正不断普及,取代沿用已久的传统 HDD 机械式硬碟,不过目前市面上绝大部份 SSD 产品,仍沿用 HDD 时代的标準规格,包括 SATA 接口及 AHCI 控制器介面,这些规格本是针对昔日慢速、高延迟的 HDD 机械式硬碟而生,无法完全发挥 SSD 低延迟、平行读写的性能优势,逐渐成为 SSD 固态硬碟性能瓶颈所在。

针对 SSD 储存装置发展, Intel 早于 2007 年 IDF 技术峰会中提出 NVMHCI (Non-Volatile Memory Host Controller Interface) 规範,并于 2008 年 4 月完成 NVMHCI 1.0 规範。紧接 2009 年下半年 NVMe (Non-Volatile Memory Express) 工作小组正式成立,确定採用 PCI Express 作为标準化接口,更取得到 90 多家公司支援, NVMe 1.0 版本技规範正式于 2011 年 3 月 1 日发布。

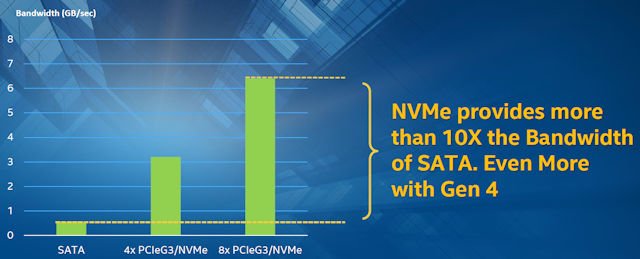

NVMe 技术规範能为所有 PCI Express 标準化接口 NAND Flash 储存装置,供高性能、可扩展的控制器介面规範,相较于主流 SATA 6Gbps 介面速度上限约 600MB/s , SATA Express 採用 PCIe Gen 3 x2 规格,频宽最高可达 1969MB/s ; M.2 及 U.2(SFF-86390 介面 ) 则支援 PCIe 3 x4 规格,最高频宽可高达 3938MB/s ;伺服器、工作站市场的 PCIe SSD 产品将进一步支援 PCIe 3 x8 规格,速度是传统 SATA 6Gbps 的 10 倍。

不过, NVMe 技术规範并非单纯的为频宽提升,而是针对 NAND Flash 特别在软体驱动层面作出改良,取代老旧的 AHCI 规格令 SSD 产品性能得以优化,大幅强化并行读写能力,满足现代 多核心 CPU 强大运算性能,例如採用较少的阶段数据传输、更深入的 Command Queues 排程、更高效率的 Interrupts Processing 中断处理。

现时,绝大部份 Intel 9 系列平台均支援 NVMe 技术规範,新一代 Intel 100 系列平台更进一步提升系统晶片的 PCIe Lanes 数目,为 NVMe 加速普及作好準备,市调机构预测 NVMe SSD 产品将会于 2016 下半年爆发性成长, 2017 年将会取代 AHCI 成为主流 SSD 标準规格, NVMe SSD 时代正式来临。

AHCI vs NVMe

儘管现时有不少高阶 SSD 产品改用 PCIe 接口,以突破 SATA 接口的频宽瓶颈,但控制器设计与 SATA 接口 SSD 一样,採用老旧的 AHCI 控制器介面,优点是大部份作业系统均已原生支援 AHCI 驱动,相容性高能支援绝多部份作业系统及主机板平台,但 AHCI 控制器介面却无法完全发挥 PCI Express 介面及 NAND Flash 颗粒的性能优势。

AHCI 控制器介面 (Advanced Host Controller Interface) 是 PCI 时代非常老旧的技术规範,主要是针对旋转碟面读写的机械式 HDD 而设,例如加入 NCQ (Native Command Queuing) 技术、优化硬碟的资料分布,将存取顺序作最有效率的排序以减少机械臂移动的距离,进而达到省时以及延长硬碟寿命的效果,但当时的设计并非为 SSD 产品而生。

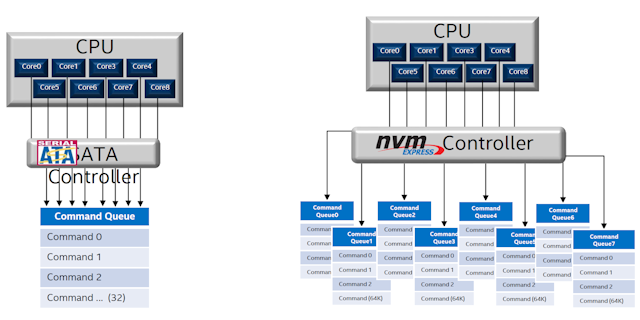

NVMe 控制器介面特别针对 PCI Express 接口及 NAND Flash 特性作出了优化, NVMe 能同时处理最高 6 万 4 千个 Command Queues 指令列,每个指令列最高可包含 6 万 4 千个指令,充分发挥 NAND Flash 平行读写优势。 AHCI 控制器介面则只能同时处理 1 个 Command Queues 指令列,每个指令列最高只能包含 32 个指令,令 IOPS 读写性能大幅落后 NVMe 。

此外, NVMe 控制器介面支援 PCIe 3.0 技术规範首次引入的 MSI-X 中断处理 (Interrupts Processing) ,并加入了 Interrupts Steering 中断导向能力。旧有的 AHCI 控制器仅支援 MSI 中断处理,装置仅获分配 1 个定址并同时只能处理 1 个中断,在多核心处理器环境下只能让单颗核心进行存取。

NVMe 控制器则最高可分配多达 2048 个 Interrupts Processing 中断处理,同时每个中断均拥有独立的目标定址,令系统不同处理器核心均能同时存取 SSD 装置,此一差异令 NVMe 与 AHCI 在 IOPS 及读写延迟上存在巨大差距。

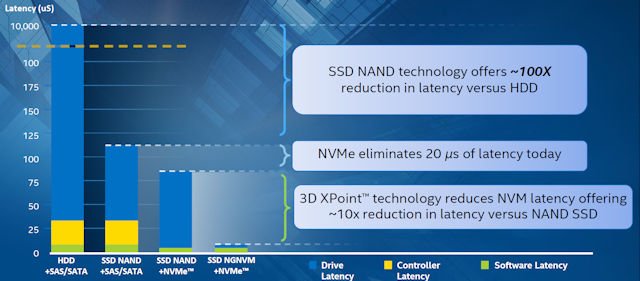

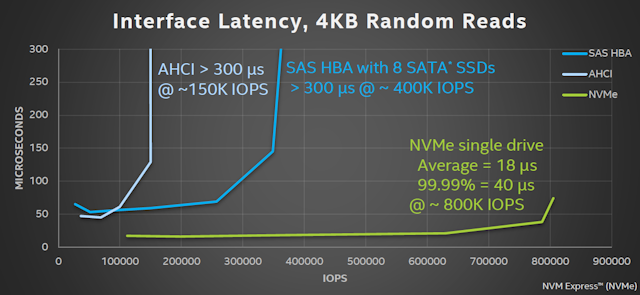

当指令所需的资料定址不在寄存器中, AHCI 控制器介面需要额外浪费 6-9 个指令週期才能完成读取,约浪费 12000 ~ 18,000 个 CPU Cycles ,造成约 2.5 ~ 4μs 的延迟,而 NVMe 控制器介面仅需额外 2 个指令,约浪费 4000 个 CPU Cycles ,令 NVMe 的 SSD 装置拥有更低延迟,减少对 CPU 资源浪费令运算性能明显提升。

比较处理大量细碎档案时, AHCI 与 NVMe 亦存在巨大性能差异, AHCI 控制器介面处理读写命令时,命令参数需进行两次无法并行的系统记忆体存取,而 NVMe 则只需要进行一次 64 Bytes 的系统记忆体存取,令 IOPS 吞吐量大幅提升。此外, AHCI 控制器介面在发出指令时需要进行同步锁定资料, NVMe 控制器则无需进行同步锁定资料,将有效提升平行读写及多线程运算性能。

就像 IDE 接口一样, SATA 连接埠与 AHCI 介面已完成历史任务,为配合未来 NAND Flash 技术发展, NVMe 控制器介面将成为未来储存介面的主流标準,基于 PCI Express 协定以不同的接口形式普及。

NVMe and AHCI Storage InterfaceComparison

AHCINVMeMaximum Queue Depth1 Command Queue32 commands per Q

64K Queues

64K Commands per Q

Un-cacheable register accesses12,000-18,000 CPU Cycles wasted~ 4,000 CPU Cycles wastedMSI-X and InterruptSingle Interrupt no Steering2048 Interrupt with Steering supportParallelism & Multiple ThreadsRequires Synchronization lockto issue commandNo Locking requiredEfficiency for 4KB Commands

Command parameter require

two serialized host DRAM fetches

Command parameters in one64 Bytes Fetch